Subtotal $0.00

Shopping cart

- Sweden, Spain, Thailand, USA

- +34 9369 444 00

- info@swedishtelecomopto.com

X

- No products in the list

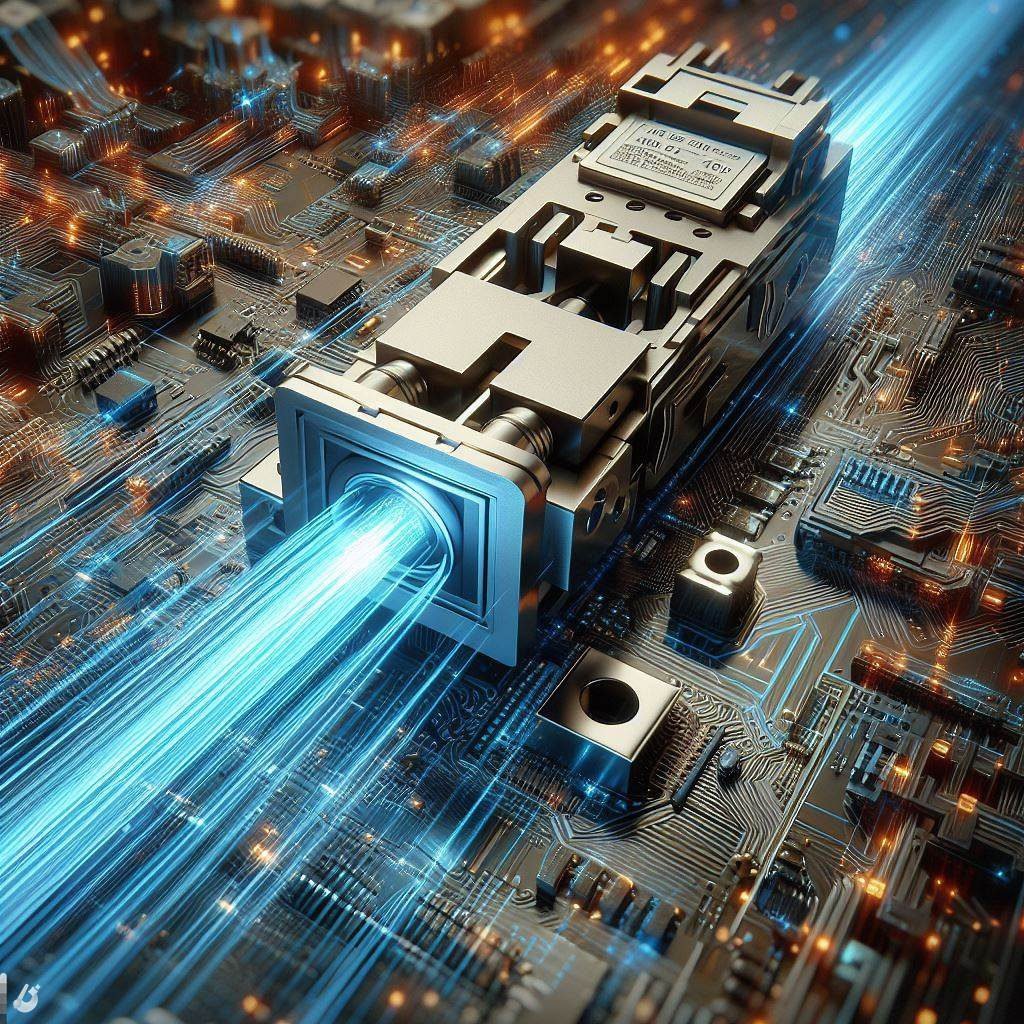

High-performance long-reach 100G QSFP28 LR4 transceiver with 28G lane support – up to 10km

The STC-QSFP28-LR4-28G is a 100G optical transceiver optimized for long-range transmission over single-mode fiber (SMF) up to 10km. It supports 4x 25Gbps electrical lanes running at 28Gbps each, with optical channels operating at LAN-WDM wavelengths: 1295.56nm, 1300.05nm, 1304.58nm, and 1309.14nm. This transceiver is compliant with QSFP28 MSA and IEEE 802.3ba 100GBASE-LR4 standards, providing exceptional performance for metro access, long-haul enterprise interconnects, and carrier-grade environments.

| Parameter | Value |

| Form Factor | QSFP28 |

| Data Rate | 4x 25Gbps @ 28Gbps electrical lanes |

| Wavelengths | 1295.56nm, 1300.05nm, 1304.58nm, 1309.14nm |

| Fiber Type | Single-Mode Fiber (SMF) |

| Reach | Up to 10km |

| Connector | LC Duplex |

| Temperature Range | 0°C to 70°C (Commercial Grade) |

| Power Consumption | < 3.5W |

| Digital Diagnostics | Yes |

| Compatibility | Cisco, Juniper, Arista, Huawei… |

This module is available in volume or with custom tuning.

👉 Request a quote or contact our optical team today. sales@swedishtelecomopto.com