Subtotal $0.00

Shopping cart

- Sweden, Spain, Thailand, USA

- +34 9369 444 00

- info@swedishtelecomopto.com

X

- No products in the list

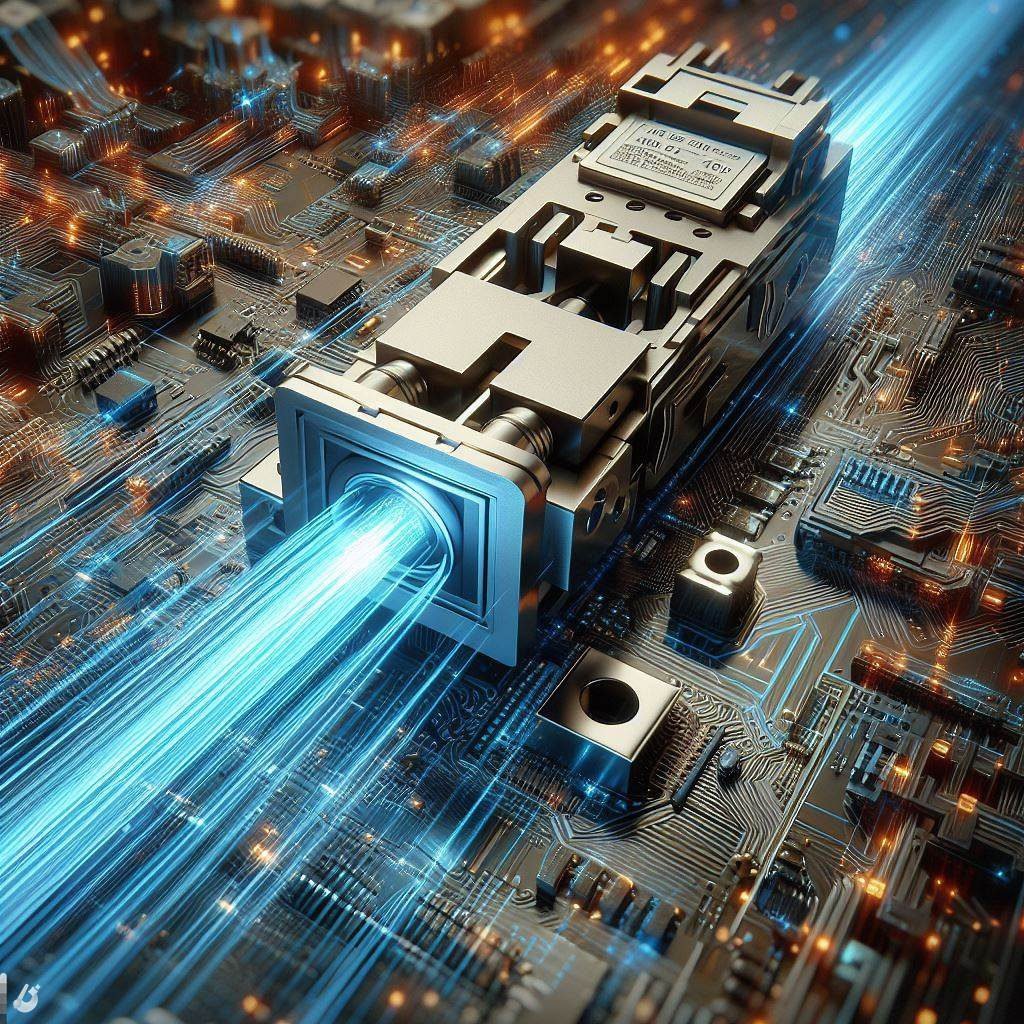

Parallel single-mode 100G QSFP28 transceiver with MPO interface – up to 2km reach

The STC-QSFP28-PSM-IR4 is a high-performance 100G optical transceiver that uses four parallel single-mode fiber pairs with MTP/MPO interface to achieve long-reach point-to-point connectivity up to 2km. It operates at four distinct CWDM wavelengths: 1271nm, 1291nm, 1311nm, and 1331nm. This module is ideal for applications requiring low-cost parallel single-mode solutions in data centers and high-performance computing environments. It is fully compliant with QSFP28 MSA and 100G PSM4 IR4 specifications.

| Parameter | Value |

| Form Factor | QSFP28 |

| Data Rate | 100Gbps (4x25Gbps) |

| Wavelengths | 1271nm, 1291nm, 1311nm, 1331nm |

| Fiber Type | Single-Mode Fiber (SMF) |

| Reach | Up to 2km |

| Connector | MTP/MPO-12 |

| Temperature Range | 0°C to 70°C (Commercial Grade) |

| Power Consumption | < 3.5W |

| Digital Diagnostics | Yes |

| Compatibility | Cisco, Juniper, Arista, Huawei… |

This module is available in volume or with custom tuning.

👉 Request a quote or contact our optical team today. sales@swedishtelecomopto.com

Check out our 100G QSFP28 SR4 LC 100M